- 您现在的位置:买卖IC网 > Sheet目录3882 > PIC16F87T-E/ML (Microchip Technology)IC MCU FLASH 4KX14 EEPROM 28QFN

192

8008H–AVR–04/11

ATtiny48/88

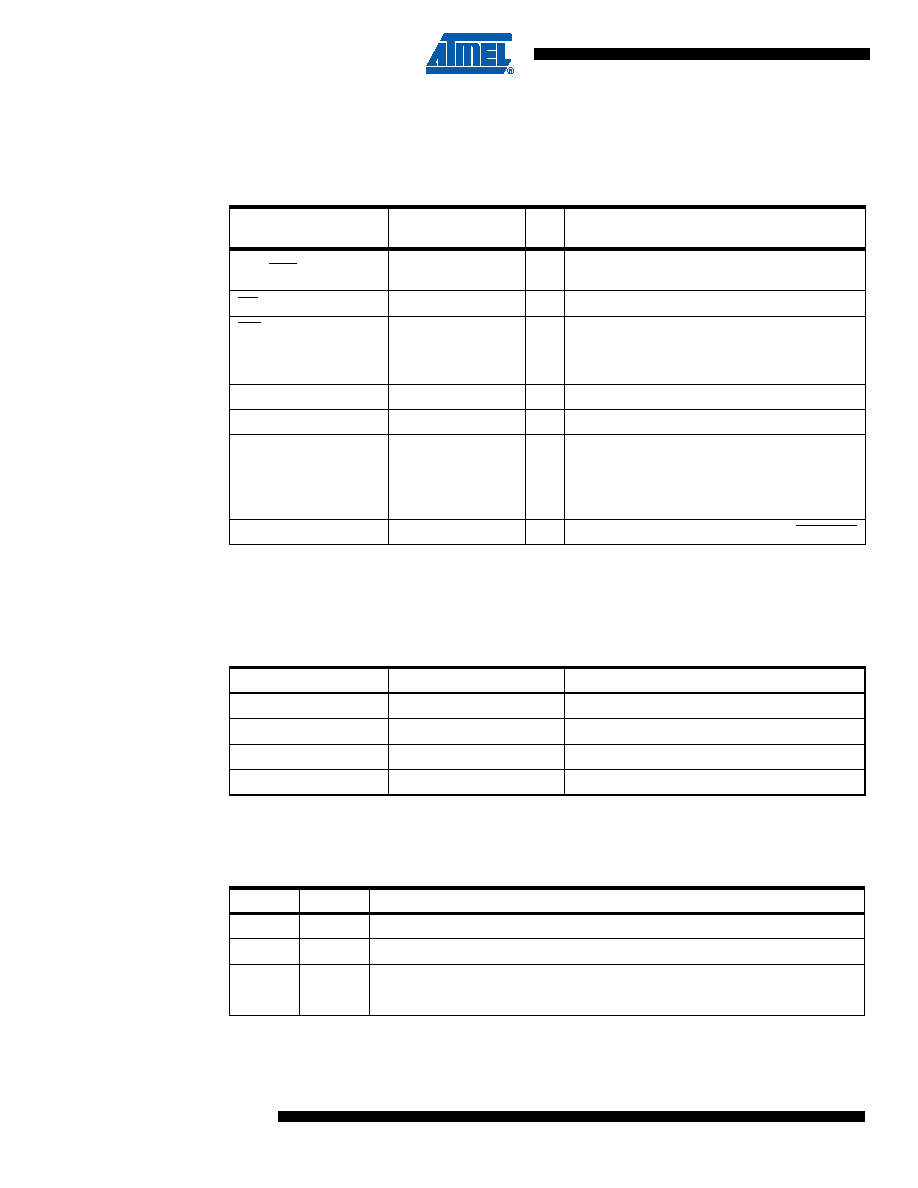

Signals are described in Table 21-3, below. Pins not listed in the table are referenced by pin

names.

Note:

VCC - 0.3V < AVCC < VCC + 0.3V, however, AVCC should always be within 4.5 – 5.5V

Pulses are assumed to be at least 250 ns, unless otherwise noted.

The XA1/XA0 pins determine the action executed when the CLKI pin is given a positive pulse.

The bit coding is shown in Table 21-5.

Table 21-3.

Pin Name Mapping

Signal Name in

Programming Mode

Pin Name

I/O

Function

RDY/BSY

PD1

O

0: Device is busy programming, 1: Device is

ready for new command

OE

PD2

I

Output Enable (Active low)

WR

PD3

I

Write Pulse (Active low)

BS1

PD4

I

Byte Select 1 (“0” selects Low byte, “1” selects

High byte)

XA0

PD5

I

XTAL Action Bit 0

XA1

PD6

I

XTAL Action Bit 1

PAGEL

PD7

I

Program memory and EEPROM Data Page

Load

BS2

PC2

I

Byte Select 2 (“0” selects Low byte, “1” selects

2’nd High byte)

DATA

{PC[1:0]: PB[5:0]}

I/O

Bi-directional Data bus (Output when OE is low)

Table 21-4.

Pin Values Used to Enter Programming Mode

Pin

Symbol

Value

PAGEL

Prog_enable[3]

0

XA1

Prog_enable[2]

0

XA0

Prog_enable[1]

0

BS1

Prog_enable[0]

0

Table 21-5.

XA1 and XA0 Coding

XA1

XA0

Action when CLKI is Pulsed

0

Load Flash or EEPROM Address (High or low address byte determined by BS1).

0

1

Load Data (High or Low data byte for Flash determined by BS1).

1

0

Load Command

1

No Action, Idle

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC16F87-E/ML

IC MCU FLASH 4KX14 EEPROM 28QFN

PIC18LF4320-I/ML

IC MCU FLASH 4KX16 EEPROM 44QFN

PIC16F77T-I/PTG

IC MCU FLASH 8KX14 W/AD 44TQFP

PIC16LF1933-I/SO

IC PIC MCU FLASH 4K 28-SOIC

PIC16C54C-20I/SO

IC MCU OTP 512X12 18SOIC

PIC16LF726-I/SO

IC PIC MCU FLASH 8K 1.8V 28-SOIC

PIC12CE673-10/P

IC MCU OTP 1KX14 A/D&EE 8DIP

PIC16F726-I/SO

IC PIC MCU FLASH 8KX14 28-SOIC

相关代理商/技术参数

PIC16F87T-E/SO

功能描述:8位微控制器 -MCU 20MHz 4K Flash RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F87T-E/SS

功能描述:8位微控制器 -MCU 20MHz 4K Flash RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F87T-I/ML

功能描述:8位微控制器 -MCU 7KB 368 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F87T-I/SO

功能描述:8位微控制器 -MCU 7KB 368 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F87T-I/SS

功能描述:8位微控制器 -MCU 7KB 368 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F882-E/ML

功能描述:8位微控制器 -MCU 3.5KB Enh FLSH 128 RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F882-E/SO

功能描述:8位微控制器 -MCU 3.5KB Enh FLSH 128 RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F882-E/SP

功能描述:8位微控制器 -MCU 3.5KB Enh FLSH 128 RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT